VLSI DESIGN - Common Path Pessimism Removal (CPPR)

In the world of Very Large Scale Integration (VLSI) design, achieving precise timing analysis is crucial to the success of a project. Designers strive for accuracy not only to ensure functionality but also to avoid the pitfalls of overdesigning, which can escalate costs and extend development timelines. One critical technique that plays a pivotal role in refining timing analysis is Common Path Pessimism Removal (CPPR).

Understanding Pessimism in Timing Analysis

Before we dive into CPPR, it’s crucial to understand the concept of pessimism in timing analysis. In the realm of VLSI, timing analysis is the process of verifying that the circuit meets specific timing requirements, such as setup and hold times. However, due to variations in manufacturing processes, operating conditions, and other factors, designers often incorporate a degree of pessimism into their timing calculations. This pessimism acts as a safety buffer, ensuring the chip operates correctly under worst-case conditions.

While some degree of pessimism is necessary, excessive pessimism can lead to overdesign. Overdesigning means incorporating more buffers, opting for faster (and more expensive) components, or implementing other design changes that, while making the design safer, also make it more costly and complex than necessary. This is where CPPR comes into play.

Common Path Pessimism Removal (CPPR)

CPPR is a sophisticated technique used to refine timing analysis by identifying and eliminating undue pessimism. Specifically, it addresses the pessimism associated with the clock paths in on-chip variation (OCV) mode analysis.

How Does CPPR Work?

Consider a typical timing path that includes both launch and capture paths. These paths might share a common segment of the clock path up to a certain point. In the absence of CPPR, different timing numbers (late and early) are applied to this shared segment, introducing unnecessary pessimism into the analysis.

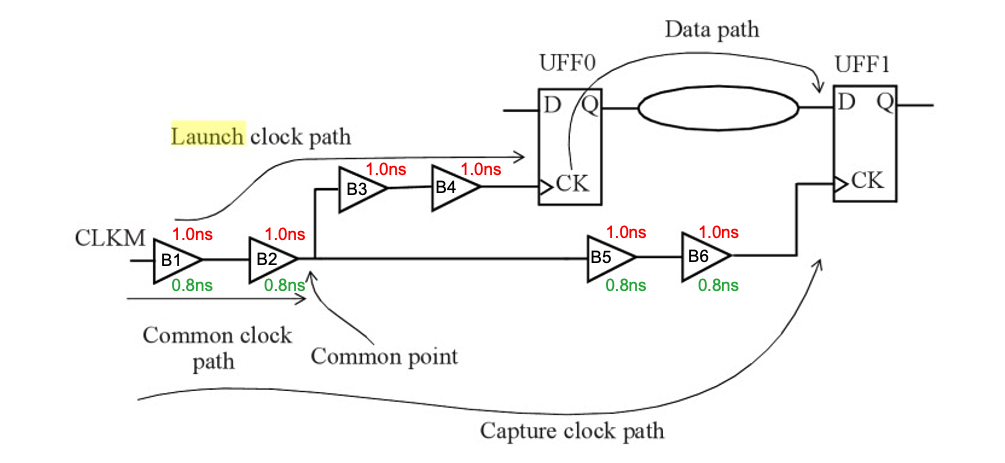

Let us consider the following example:

In the given scenario, the numbers in red represent the maximum delays, while the numbers in green represent the minimum delays. So for setup timing, the launch clock path has a delay of 4.0 ns (B1 -> B2 -> B3 -> B4), while the capture clock path has a delay of 3.2 ns (B1 -> B2 -> B5 -> B6). So the clock skew is 0.8 ns.

However, the shared segment (B1 -> B2) is analyzed with different timing numbers, leading to pessimism. Thus, removing this pessimism is necessary to avoid overdesign.

In this example, the CPPR Adjustment is 0.4 ns, which is the difference between the maximum (2.0ns) and minimum delays (1.6ns) in the shared segment. By removing this pessimism, the clock skew will be adjusted to 0.4 ns, instead of the 0.8 ns skew that was previously assumed.

CPPR scrutinizes these shared segments and adjusts the timing analysis to reflect a more realistic scenario. It essentially corrects the skew between the clock paths, thereby reducing the pessimism and, consequently, the likelihood of overdesign.

The Impact of CPPR

The application of CPPR can have a profound impact on the design process:

Improved Accuracy: By removing undue pessimism, CPPR leads to more accurate timing analysis. This accuracy is crucial for making informed design decisions.

Cost Efficiency: Reducing overdesign directly translates to cost savings. With CPPR, designers can opt for components that meet the actual requirements without the added expense of unnecessary safety buffers.

Enhanced Performance: By avoiding the insertion of unnecessary buffers or other elements, CPPR can lead to designs that are not only more cost-effective but also potentially faster and more efficient.

Implementing CPPR

Most modern Electronic Design Automation (EDA) tools incorporate features that enable CPPR. Designers can selectively apply CPPR to their timing analysis, ensuring that the benefits are realized without compromising the integrity of the design. It’s worth noting that the effectiveness of CPPR depends on the complexity of the design and the specific challenges it faces. As such, a deep understanding of the design and the timing analysis process is essential to leverage CPPR effectively.